## UNIVERSITY OF TWENTE.

# **Exam Computer Systems/Computer** Architecture and Organisation Bachelor 2<sup>nd</sup> year, EE and CS, EWI

Module/course code: Computer Systems 201400210(CS) / 201400217(EE)

|                                     | :                                                                                                                                                                                                          | 27 September 2019 13:45-15:30 (+25% for students who may use extra time) or: A.B.J. Kokkeler E. Molenkamp / A.B.J. Kokkeler |  |  |  |  |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                     | of test: Clos<br>ed aids durir                                                                                                                                                                             | ed book<br>ng the test: Writing materials, simple calculator                                                                |  |  |  |  |

| 27 qu                               | estions on 8 pag                                                                                                                                                                                           | ges and 4 pages with the ARC documentation                                                                                  |  |  |  |  |

| Instru                              | ctions for this e                                                                                                                                                                                          | examination:                                                                                                                |  |  |  |  |

| 1.                                  | Scientific or graphical calculators, laptops, mobile phones, books etc. are not allowed. Put those in your bag now (and switched off)!                                                                     |                                                                                                                             |  |  |  |  |

| 2.                                  | Write your answers on this paper, in the provided boxes, and hand in this exam <b>and</b> the multiple choice form (even when you did not answer any questions).                                           |                                                                                                                             |  |  |  |  |

| 3.                                  | All multiple ch                                                                                                                                                                                            | oice questions have exactly one correct answer; place an X in the correct box and copy the multiple choice form.            |  |  |  |  |

| 4.                                  |                                                                                                                                                                                                            | hoice form is scanned and automatically corrected. Make sure to fill in that form                                           |  |  |  |  |

|                                     | •                                                                                                                                                                                                          | xcept for the "docent / teacher" part).                                                                                     |  |  |  |  |

| 5.                                  | For grading th                                                                                                                                                                                             | e exam, correction for guessing is used.                                                                                    |  |  |  |  |

| 6.                                  | Exactly 1 answ                                                                                                                                                                                             | ver is correct. No answer given is counted as an incorrect answer.                                                          |  |  |  |  |

| 7.                                  | Write your na                                                                                                                                                                                              | me, student number and educational programme at the bottom of this page.                                                    |  |  |  |  |

| 8.                                  | The documentation refers to the ARC processor. If a problem indicates that it is about the <b>subset ARC</b> processor then only the instructions listed in figure 5-2 (documentation page 2) may be used. |                                                                                                                             |  |  |  |  |

| Logic                               | symbols: <b>not</b>                                                                                                                                                                                        | <b>a</b> is also represented as $\overline{a}$ , <b>a'</b> , ! <b>a</b> , # <b>a</b>                                        |  |  |  |  |

|                                     | a ar                                                                                                                                                                                                       | nd b is also represented as a.b, a&b                                                                                        |  |  |  |  |

| a or b is also represented as a + b |                                                                                                                                                                                                            |                                                                                                                             |  |  |  |  |

|                                     | а хо                                                                                                                                                                                                       | or <b>b</b> is also represented as $a \oplus b$                                                                             |  |  |  |  |

| (please                             | e underline your f                                                                                                                                                                                         | family name (i.e., the name on your student card), so that we know how to sort))                                            |  |  |  |  |

| Name                                | :                                                                                                                                                                                                          |                                                                                                                             |  |  |  |  |

| Stude                               | nt number:                                                                                                                                                                                                 |                                                                                                                             |  |  |  |  |

Educational programme (EE, TCS, ..): .....

#### Question 1

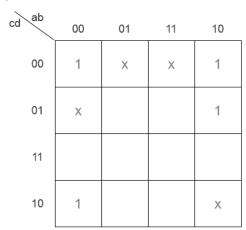

What is the simplified Boolean equation for this Karnaugh map?

X denotes a don't care term and the fields that are not filled in are 0.

- a□ b'.d'

- $b\Box$  b'.d' + b'.c'

- $c \square$  b'.d' + a'.b'.c'.d'

- $d\Box$  b'.d' + b'.c'+ c'.d'

#### **Question 2**

What is the simplified Sum of Product of the Boolean expression

(a + b).(a' + b + c)

- a□ a.b + c

- $b\Box$  b.(a'+ c)

- $c\square$  b + a.c

- $d\square$  a.c + a.b + a'.b

#### **Question 3**

What is the minterm expansion of F(P,Q,R) = P.Q + Q.R' + P.R'

- $a \square \qquad \sum m(2,4,6,7)$

- $b \square \qquad \sum m(0,1,3,5)$

- $c \square \qquad \sum m(0,1,6,7)$

- $d\Box \qquad \sum m(2,3,4,5)$

## **Question 4**

What is the minimum number of gates required to implement the Boolean function (A.B+C) if only 2-input NAND gates are used?

- a□ 2

- b□ 3

- $c \square \qquad 4$

- d□ 5

## **Question 5**

What is the hexadecimal representation of octal 3657 ?

- a□ 7AF

- b□ D78

- c□ D71

- d□ 32F

| Name:   | <br> | <br> | <br>_ |

|---------|------|------|-------|

| St. nr: |      |      |       |

#### **Question 6**

Given is a normalized floating point representation in base 2. The bit pattern from left to right is: Sign bit: 1 bit (1 is negative, 0 is positive), Exponent field: 7 bits in excess 64, Fraction field: 8 bits (not included is the hidden bit). Point is right of hidden bit.

Only when the exponent field is filled with all zeros, the representation is not normalized. In that case the decimal number 0 is represented, independent of the sign and fraction field.

a□

с□

| What is the hexadecimal representation        | a□ | 4314 |

|-----------------------------------------------|----|------|

| of decimal $8\frac{5}{8}$ (use rounding style | b□ | 40A0 |

| truncation) in this floating point            | _  |      |

| representation?                               | c□ | 2F1A |

|                                               | d□ | 2A13 |

## **Question 7**

| Given the floating point representation as defined in question 6. What is the | a□ | 2 <sup>126</sup>                     |

|-------------------------------------------------------------------------------|----|--------------------------------------|

| maximum positive decimal value that can                                       | b□ | 2 <sup>127</sup>                     |

| be represented?                                                               | c□ | 2 <sup>63</sup> (1-2 <sup>-9</sup> ) |

|                                                                               | Ч□ | 2 <sup>63</sup> (2-2 <sup>-8</sup> ) |

#### **Question 8**

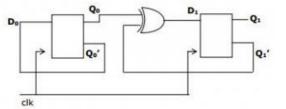

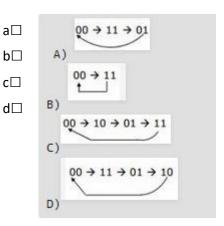

The Data flip-flops in this schematic are positive edge triggered. Each state is designated as a two bit string Q<sub>0</sub>Q<sub>1</sub>. Let the initial state be 00.

Note:  $Q_0$  is left bit of the state.

What is the state transition sequence?

Name:\_\_\_\_\_\_ St. nr:

#### **Question 9**

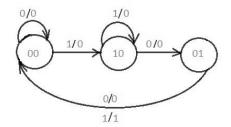

This Finite State Machine is realized with 2 data flip-flops  $(Q_1Q_0)$  and combinational logic. **Note:**  $Q_1$  is left bit of the state. The input is X and the output is Y. For the state  $Q_1Q_0$ =11 the behavior is undefined. What is the Boolean equation for the data input  $(D_1)$  of  $Q_1$ ?

#### **Question 10**

Given is the Finite State Machine of question 9. What is a Boolean equation for the output Y?

$a\square$  Y = (Q<sub>1</sub>' + Q<sub>0</sub>).X

$b\square$   $Y = Q_1.X$

a□

b□

c□ d□  $D_1 = Q_1.X + Q_1'.Q_0'$

$D_1 = Q_0 + Q_1'.X$

$D_1 = Q_1'.Q_0'$

$D_1 = Q_0'$  .X

$c\square$   $Y = Q_1'.Q_0.X$

$d\square$  Y =  $Q_1'.Q_0.+ X$

#### **Question 11**

| $Q_1$ | $Q_0$ | $Q_1^+$ | $Q_0^+$ |

|-------|-------|---------|---------|

| 0     | 0     | 0       | 1       |

| 0     | 1     | 1       | 0       |

| 1     | 0     | 1       | 1       |

| 1     | 1     | 1       | 1       |

The table above is a 2 bit saturating upcounter. The counter is built as a synchronous sequential circuit using D flip-flops. The Boolean equations for the data input  $D_1$  (input of flip-flop  $Q_1$ ) and  $D_0$  (input of flip-flop  $Q_0$ ) are:

## $a \square$ $D_1=Q_1+Q_0$ and $D_0=Q_1+Q_0'$

$$b\square$$

$D_1=Q_1'$ .  $Q_0$  and  $D_0=Q_1'+Q_0'$

$$c\Box$$

$D_1=Q_1+Q_0'$  and  $D_0=Q_1+Q_0$

$d\square$  none of these

## **Question 12**

The worst case delay of the full adders used in a carry ripple adder is 2 ns (from any input to any output). What is approximately the worst case delay of an N bit ripple carry adder?

- a □  $log_2(N) \times 2 ns$

- $b \square N^2 \times 2 \text{ ns}$

- $c\square$  N × 2 ns

- $d\square$  None of these

| Name:                                                                                      |    | UNIVERSITY OF TWEN                                                                                               |

|--------------------------------------------------------------------------------------------|----|------------------------------------------------------------------------------------------------------------------|

| St. nr:                                                                                    |    |                                                                                                                  |

| Question 13                                                                                |    |                                                                                                                  |

| The timing properties of a Data flip-flop are: setup time (Tsu) is 3 ns, Hold time (Th) is | a□ | For a correct behavior the data input must be stable 3 ns before until 1 ns before the active edge of the clock. |

| -1 ns, clock to output delay (Tco) is 2.5 ns. What is correct?                             | b□ | The output is stable 1.5 ns after the active edge of the clock.                                                  |

|                                                                                            | c□ | A negative time for the hold time is not valid.                                                                  |

|                                                                                            | d□ | none of these                                                                                                    |

| Question 14                                                                                |    |                                                                                                                  |

| What is an ARC assembly instruction that                                                   | a□ | orn %r0, %r0, %r1                                                                                                |

| has as behavior that the contents of %r1 becomes decimal -1?                               | b□ | ld [%r0-1], %r1                                                                                                  |

| Representation is twos complement.                                                         | с□ | sethi -1, %r1                                                                                                    |

|                                                                                            | d□ | None of these                                                                                                    |

| Question 15                                                                                |    |                                                                                                                  |

| .begin<br>.org 0<br>ld[x], %r1                                                             | a□ | In main memory the contents at decimal address 24 has decimal value 10.                                          |

| orn %r0, %r1, %r1                                                                          | b□ | The decimal value of label over is decimal 5.                                                                    |

| addcc %r1,1,%r1<br>bneg over                                                               | c□ | The instruction halt is at hexadecimal address                                                                   |

16.

None of these.

$\mathsf{d}\square$

After the execution of this program, what is correct?

#### **Question 16**

over:

x: .end bneg over

st %r1, [x]

halt

-10

| .begin    |           |                | a□ | srl   | %r1, 4, %r1   |

|-----------|-----------|----------------|----|-------|---------------|

| org 0     |           |                | uШ | 311   | 7011, 4, 7011 |

| sethi     | series,%  |                | b□ | srl   | 1, %r1, %r1   |

|           | srl       | %r1,10,%r1     |    |       |               |

|           | addcc     | %r0, 0, %r11   | c□ | addcc | %r1, 4, %r1   |

| lp:       | ld        | [%r1], %r10    |    |       |               |

|           | addcc     | %r10,%r0,%r0   | d□ | addcc | %r1, 1, %r1   |

|           | be        | rdy            |    |       |               |

|           | addcc     | %r10,%r11,%r11 |    |       |               |

|           | ???????   | ?              |    |       |               |

|           | ba        | lp             |    |       |               |

| rdy:      | halt      |                |    |       |               |

| series: 1 | L,2,3,4,0 |                |    |       |               |

|           | .end      |                |    |       |               |

|           |           |                |    |       |               |

This program should accumulate the 32-bit integer values in the list with start address series. The list is terminated with decimal 0. What instruction should be inserted on the line with ????????

| Name    | : | <br> | <br> |

|---------|---|------|------|

| St. nr: |   |      | <br> |

## **Question 17**

The ARC processor is extended with instruction FUN. The micro program of the execution phase of FUN is given below.

| TOW IS given below. |        |      |        |      |        |      |    |    |         |         |      |

|---------------------|--------|------|--------|------|--------|------|----|----|---------|---------|------|

| address             | А      | Amux | В      | Bmux | С      | Cmux | Rd | Wr | ALU     | Cond    | Jump |

|                     |        |      |        |      |        |      |    |    |         |         | addr |

| 1792                | _      | 1    | %r0    | 0    | %temp0 | 0    | 0  | 0  | addcc   | next    | -    |

|                     |        |      |        |      |        |      |    |    |         | address |      |

| 1793                | _      | 1    | _      | _    | %temp1 | 0    | 0  | 0  | lshift2 | Next    | -    |

|                     |        |      |        |      |        |      |    |    |         | address |      |

| 1794                | %temp0 | 0    | %temp1 | 0    | -      | 1    | 0  | 0  | addcc   | Jump    | 2047 |

|                     |        |      |        |      |        |      |    |    |         |         |      |

| What is correct?                                 | After execution of FUN the contents of %temp0 is always 0 |                                                      |                                                                                                          |           |                                             |  |  |

|--------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------|---------------------------------------------|--|--|

|                                                  | b□                                                        | The contents of %temp0 and %temp1 is always the same |                                                                                                          |           |                                             |  |  |

|                                                  | c□                                                        | The f                                                | RTL behavior of this                                                                                     | instruc   | tion is: $R[rd] \leftarrow 3 \times R[rs1]$ |  |  |

|                                                  | d□                                                        | The f                                                | RTL behavior of this                                                                                     | s instruc | tion is: $R[rd] \leftarrow 5 \times R[rs1]$ |  |  |

| Question 18                                      |                                                           |                                                      |                                                                                                          |           |                                             |  |  |

| What is the bit patter                           | n of                                                      | a□                                                   | 000000                                                                                                   |           |                                             |  |  |

| the <i>field op3</i> in the machine code of an A | .RC                                                       | b□                                                   | 000001                                                                                                   |           |                                             |  |  |

| instruction when the                             | start                                                     | с□                                                   | 000010                                                                                                   |           |                                             |  |  |

| address in the micro s is decimal 1792?          | store                                                     | d□                                                   | None of these                                                                                            |           |                                             |  |  |

|                                                  |                                                           |                                                      |                                                                                                          |           |                                             |  |  |

| Question 19                                      |                                                           |                                                      |                                                                                                          |           |                                             |  |  |

| What is correct?                                 |                                                           | a□                                                   | Memory-mapped I/O uses a single address space to address both memory and I/O devices.                    |           |                                             |  |  |

|                                                  |                                                           | b□                                                   | A processor that supports memory-mapped I/O has different read and write instructions for IO and memory. |           |                                             |  |  |

|                                                  |                                                           | c□                                                   | A computer based on the <i>von Neumann model</i> has no Control Unit.                                    |           |                                             |  |  |

|                                                  |                                                           | d□                                                   | The register in a processor with name <i>program counter</i> counts the number of instructions executed. |           |                                             |  |  |

|                                                  |                                                           |                                                      |                                                                                                          |           |                                             |  |  |

| Question 20                                      |                                                           |                                                      |                                                                                                          |           |                                             |  |  |

| Given two processors                             |                                                           |                                                      |                                                                                                          | a□        | 89AB                                        |  |  |

| byte-organized memore<br>Endian addressing an    | -                                                         |                                                      |                                                                                                          | b□        | BA98                                        |  |  |

| addressing. Processor                            |                                                           |                                                      | -                                                                                                        | с□        | AB89                                        |  |  |

| Processor B reads dat<br>Processor A. What is    |                                                           |                                                      | •                                                                                                        | d□        | A98B                                        |  |  |

| Processor A wrote (he                            |                                                           |                                                      | o. D When                                                                                                |           |                                             |  |  |

| Name:                                                                        |                                                                                                               |                                                                                                                                               |                                                      | UNIVERSITY OF TWENTE.                           |  |

|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------------------------------------------|--|

| St. nr:                                                                      |                                                                                                               |                                                                                                                                               |                                                      |                                                 |  |

| Question 21                                                                  |                                                                                                               |                                                                                                                                               |                                                      |                                                 |  |

| What is correct?                                                             | а□                                                                                                            |                                                                                                                                               | ern processor the progra<br>ed for reading the keybo | ·                                               |  |

|                                                                              | b□                                                                                                            | In the inte                                                                                                                                   | ·                                                    | processor interrupts the                        |  |

|                                                                              | c□                                                                                                            |                                                                                                                                               | errupt I/O technique the of a device.                | processor is polling for an                     |  |

|                                                                              | d□ DMA is a technique for transferring data between memory and external device with minimal involver the CPU. |                                                                                                                                               |                                                      |                                                 |  |

| Question 22                                                                  | interrunt scens                                                                                               | ario and acc                                                                                                                                  | ume an interrunt canno                               | <b>t</b> suspend other interrupts:              |  |

| Task                                                                         | Service time                                                                                                  | ario ario ass                                                                                                                                 | Maximum allowed latency                              | Maximum Frequency                               |  |

| A                                                                            | 10 ms                                                                                                         |                                                                                                                                               | 15 ms                                                | 1/(100 ms)                                      |  |

| В                                                                            | 20 ms                                                                                                         |                                                                                                                                               | 35 ms                                                | 1/(200 ms)                                      |  |

| С                                                                            | 40 ms                                                                                                         |                                                                                                                                               | 200 ms                                               | 1/(400 ms)                                      |  |

| D                                                                            | 50 ms                                                                                                         |                                                                                                                                               | 200 ms                                               | 1/(500 ms)                                      |  |

| What is correct?                                                             | a□                                                                                                            | Maximum                                                                                                                                       | n allowed latencies for al                           | I the tasks are met                             |  |

|                                                                              | b□                                                                                                            | Task D ca                                                                                                                                     | n prevent task A being se                            | erviced in time                                 |  |

|                                                                              | c□                                                                                                            | Task A car                                                                                                                                    | n prevent task C being se                            | erviced in time                                 |  |

|                                                                              | d□                                                                                                            | None of t                                                                                                                                     | he these                                             |                                                 |  |

| addressable. I/O mappe<br>contains an Ethernet co<br>specifications concerni | ed I/O is used. Vontroller, videong addressing.                                                               | When pin <i>N</i><br>-RAM and a                                                                                                               | a Wifi controller accordir                           | es are selected. The system ng to the following |  |

| Ethernet contro                                                              | oller:                                                                                                        |                                                                                                                                               | he lowest addresses of t                             | _                                               |  |

| Video-RAM:<br>Wifi controller:                                               |                                                                                                               | <ul><li>256 KB directly following the area for the Ethernet controller.</li><li>4 MB at the highest addresses of the address range.</li></ul> |                                                      |                                                 |  |

Shadowing is not allowed.

The signals to select the different areas are respectively SelEth, SelVideo en SelWifi.

The bits of the address bus are  $A_{N-1}..A_0$  (N is number of address lines, right most bit has index 0)

| What is the equation for SelEth? | a□ | SelEth = !A <sub>22</sub> & !A <sub>21</sub> & !A <sub>20</sub> & A <sub>19</sub> & !M/in |

|----------------------------------|----|-------------------------------------------------------------------------------------------|

|                                  | b□ | SelEth = !A <sub>22</sub> & !A <sub>21</sub> & !A <sub>20</sub> & !M/in                   |

|                                  | c□ | SelEth = !A <sub>23</sub> & !A <sub>21</sub> & !A <sub>20</sub> & A <sub>19</sub> & !M/in |

|                                  | d□ | SelEth = $!A_3 \& !A_2 \& !A_1 \& A_0 \& !M/in$                                           |

| Name:                                                                                                                                                                         |                                                                                                                                 | UNIVERSITY OF TWENT                                                                                            |                      |                                                       |                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------|----------------------------------------------------|

| St. nr:                                                                                                                                                                       |                                                                                                                                 |                                                                                                                |                      |                                                       |                                                    |

| <b>Question 24</b> See question 23.                                                                                                                                           |                                                                                                                                 |                                                                                                                |                      |                                                       |                                                    |

| What is the equatio                                                                                                                                                           | n for a□                                                                                                                        | SelVideo = !A <sub>22</sub> &                                                                                  | !A <sub>21</sub> & A | A <sub>20</sub> & !A <sub>19</sub> & !A <sub>18</sub> | & !A <sub>17</sub> &!M/In                          |

| SelVideo ?                                                                                                                                                                    | b□                                                                                                                              | SelVideo = !A <sub>22</sub> & !A <sub>21</sub> & A <sub>20</sub> & !A <sub>19</sub> & !A <sub>18</sub> & !M/In |                      |                                                       |                                                    |

|                                                                                                                                                                               | c□                                                                                                                              | SelVideo = $(!A_{22} + !A_{21} + A_{20} + !A_{19} + !A_{18} + !A_{17}) \& !M/In$                               |                      |                                                       |                                                    |

|                                                                                                                                                                               | d□                                                                                                                              | SelVideo = !A <sub>22</sub> & !A <sub>21</sub> & A <sub>20</sub> & !A <sub>19</sub> & !M/In                    |                      |                                                       |                                                    |

| Question 25 A 16-bits microproced Address space: Primary cache:  For the primary cache with the tag in the cache a byte in a word. Note What are the bit nurset in the cache? | 4 MB, Byte-ad<br>Size: 16 KB (e<br>Slotsize: 512<br>Organisation:<br>e, a byte-addres<br>ache, selection o<br>e: the right most | ddressing xcluding tags) B 4-way set-associat is split into parts the face of the cache, the bit has number 0. | ive<br>hat are       | used for, respec                                      | tively, comparison<br><i>slot</i> and selection of |

| <b>Question 26</b><br>See question 25                                                                                                                                         |                                                                                                                                 |                                                                                                                |                      |                                                       |                                                    |

| What are the bit numbers of the a                                                                                                                                             |                                                                                                                                 | dress that selects                                                                                             | a□                   | 7, 6, 5, 4, 3, 2, 1                                   |                                                    |

| word in a slot?                                                                                                                                                               |                                                                                                                                 |                                                                                                                | b□                   | 8, 7, 6, 5, 4, 3,                                     |                                                    |

|                                                                                                                                                                               |                                                                                                                                 |                                                                                                                | с□                   | 9, 8, 7, 6, 5, 4,                                     | 3, 2, 1                                            |

|                                                                                                                                                                               |                                                                                                                                 |                                                                                                                | d□                   | 9, 8, 7, 6, 5, 4,                                     | 3, 2                                               |

| Question 27 A dynamic RAM chip bits. Using multiple of in total 1024 Mby width is 32 bits. How many columns width) and how man                                                | of these chips, a<br>ytes has to be bu<br>(to establish the                                                                     | memory module uilt. The word                                                                                   | a□<br>b□<br>c□<br>d□ | columns: 16 columns: 16 columns: 32 columns: 8        | rows: 8 rows: 4 rows: 4 rows: 8                    |

contain?